惠州市岚方实业有限公司

电话:400-6296-898

传真:0752-2042189

邮箱:sales@lanfsy.com

地址:惠州市博罗县罗阳镇西北路8号

邮编:516100

阻抗匹配原理详解

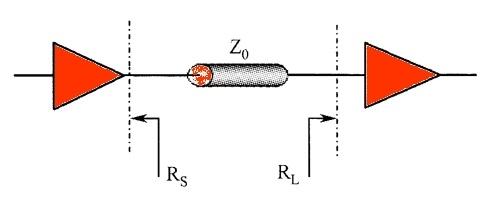

阻抗匹配(Impedancematching)是微波电子学的一部分,也是射频电路中非常重要的一部分,主要用于传输线路中,以达到能够将所有高频微波信号传输到负载点的目的。回溯到原点,提高能源效率。

一般来说,阻抗匹配有两种:改变阻抗力(聚合电路匹配)和调整传输线的波长(传输线匹配)。要匹配一组线,首先将负载点的阻抗值归一化,除以传输线的特征阻抗值,然后将这些值绘制在史密斯圆图上。

改变阻抗力如果你在负载上串联一个电容或电感来增加或减少负载的阻抗,图表上的点会跟随一个圆圈,代表实际电阻。当您将电容器或电感器接地时,图形上的点首先从图形中心旋转180 度,然后沿着电阻圆移动,然后从中心旋转180 度。可以通过重复上述方法完成匹配,直到电阻值为1,然后直接将阻抗改为0。

调整传输线将传输线从负载点拉长到源点,图上的点沿着图的中心逆时针移动,直到到达一个电阻值为1的圆圈,然后是电容或电感的阻抗增加。调整为0 以完成匹配。阻抗匹配是指传输功率大,在电源的情况下,当内阻与负载相同时,输出功率最大,此时阻抗匹配。最大功率传输定理是在高频没有反射波。对于典型的宽带放大器,输出阻抗为50,在功率传输电路中应考虑阻抗匹配,但如果信号波长远大于电缆长度,即如果电缆长度可以忽略不计,则没有需要考虑阻抗匹配。阻抗匹配是指在传输能量时,负载阻抗必须等于传输线的特性阻抗,此时传输不会引起反射,也就是说能量全部被负载吸收。相反,在传输过程中存在能量损失。高速PCB布线时,线路阻抗为50欧,防止信号反射。这是一个大概的数字,一般来说,同轴电缆的基带是50欧,频带是75欧,双绞线是100欧,为了匹配方便,只是一个整数。阻抗与电阻并不完全一样。这里只有一个抵抗的词是相同的,另一个词的抵抗是什么?简单来说,阻抗就是电阻加电抗,所以叫阻抗,简单来说,阻抗就是电阻、容抗、感抗相对于一个向量的总和。在直流电的世界里,物体阻挡电流的作用称为电阻,虽然世界上所有的材料都有电阻,但只有电阻的区别。电阻低的材料称为良导体,电阻高的材料称为绝缘体,近来高科技领域称为超导体的称为电阻值接近于零的物体。但是,在交流电领域中,电容和电感除了阻碍电流流动的电阻外,还会阻碍电流的流动,这些作用称为电抗,意思是对电流的抵抗作用。电容器和电感器的电抗分别称为容抗和感抗,分别称为容抗和感抗。测量单位是欧姆,就像电阻一样,它的值与交流电的频率有关。另外,容抗和感抗还有一个相位角的问题,相位角是一个向量的关系,所以说阻抗是向量的电阻和电抗之和。阻抗匹配是指通过匹配负载阻抗和激励源的内部阻抗来获得最大输出的工作状态。对于不同特性的电路,匹配条件是不同的。在纯电阻电路中,当负载电阻等于激励源的内阻时输出功率最大,这种工作状态称为匹配,否则称为失配。当激励源的内阻和负载阻抗中含有电抗分量时,为使负载获得最大功率,负载阻抗和内阻必须具有相同的共轭关系,即电阻分量必须相同, 和电抗分量具有相同的值和相反的符号。这种匹配条件称为共轭匹配。

阻抗匹配的研究高速设计中的阻抗匹配与信号质量有关。阻抗匹配技术丰富多样,但如何在特定系统中合理应用它们需要测量许多因素。例如,我们系统设计的很大一部分是源段的系列匹配。在什么情况下需要匹配,使用哪种匹配方法,为什么使用这种方法。

例如,大多数差分匹配采用终端匹配,时钟采用源匹配。

a、串联终端匹配串联终端匹配的理论起点是信号源端的阻抗是信号源端的阻抗等于传输线的特性阻抗,而输出端的阻抗等于传输线的特性阻抗。源端等于传输线的输出阻抗,匹配抑制来自负载端的反射信号的再反射。信号传输后,串联端匹配具有以下特点: 在串联匹配电阻的影响下,驱动信号以50%的幅度传播到负载侧。在负载侧,信号的反射系数接近+1,因此反射信号的幅度接近原始信号幅度的50%。反射信号与源端传播的信号重叠,因此负载端接收到的信号约等于原始信号幅度。信号;信号传播到源端,到达源端后被匹配电阻吸收。反射信号到达源端后,源端驱动电流降至零,直到下一次信号传输。与并联匹配相比,串联匹配不需要信号驱动器的大电流驱动能力。选择串联端匹配电阻值的原则很简单。即匹配电阻值与驱动器输出阻抗之和必须等于传输线的特性阻抗。理想信号驱动器的输出阻抗为零,但实际驱动器的输出阻抗总是相对较小,并且输出阻抗会随着信号电平的变化而变化。例如,电源电压为+4.5V 的CMOS 驱动器在低电平时的典型输出阻抗为37,在高电平时的典型输出阻抗为45 [4]。 TTL 驱动器与CMOS 驱动器相同,输出阻抗随信号电平而变化。所以对于TTL 或CMOS 电路,不可能有非常精确的匹配电阻,只能被认为是一种折衷方案。链式拓扑中的信号网络不适合串行终端,所有负载都必须连接在传输线的末端。可以看到有一段时间负载端的信号幅度是原始信号幅度的一半。显然,此时信号处于不确定的逻辑状态,信号的噪声容限非常低。系列注册是最常见的终止注册方法。它的优点是功耗低,驱动器上没有额外的直流负载,信号和地之间没有额外的阻抗,并且只需要一个电阻元件。b、并联终端匹配并联端接匹配的理论起点是在信号源级阻抗较小的情况下,增加并联电阻以匹配负载级的输入阻抗和传输线的特性阻抗。消除负载端的反射。实现形式分为单电阻和双电阻两种形式。并联终端匹配后的信号传输具有以下特点: 驱动信号沿传输线以几乎全幅值传播。所有反射都被匹配电阻吸收。负载端接收到的信号幅度近似为源端发送信号的幅度。在实际电路系统中,芯片的输入阻抗非常高,因此在单个电阻的情况下,负载的并联电阻值应接近或等于传输线的特性阻抗。假设传输线的特性阻抗为50,则R值为50。如果信号的高电平为5V,则信号的静态电流为100mA。由于典型的TTL 或CMOS 电路的驱动能力很小,这种单电阻并联匹配在这些电路中很少见。双电阻形式的并联匹配,也称为戴维南终端,比单电阻形式需要更少的电流驱动能力。这是因为两个电阻的并联值与传输线的特性阻抗相匹配,每个电阻都大于传输线的特性阻抗。考虑到芯片的驱动能力,两个电阻阻值的选择应遵循三个原则:两个电阻的并联值等于传输线的特性阻抗,阻值信号接通时驱动电流过大给电源在低电平时不宜过小,以免过大,与地相连的电阻值也小;

并联终端匹配的优点是简单易实现;明显的缺点是它引入了直流功耗:单个电阻的直流功耗是否与信号的占空比密切相关?双电阻模式无论信号是高电平还是低电平,都有直流功耗。因此,它不适用于高功耗的系统,例如电池供电的系统。此外,由于驱动能力的问题,一般的TTL和CMOS系统中不采用单电阻法,而双电阻法需要两个元件,需要在PCB上制作产品,因此对于高密度印刷电路板来说也是如此。当然,也有交流终端匹配和基于二极管的电压钳位等匹配方法。

[声明]文章版权归原作者所有,内容为作者个人观点,本站只提供参考并不构成任何投资及应用建议,转载目的在于传递更多信息,并不代表本站赞同其观点和对其真实性负责。如涉及作品内容、版权和其它问题,请在30日内与本网联系,我们将在第一时间删除内容!